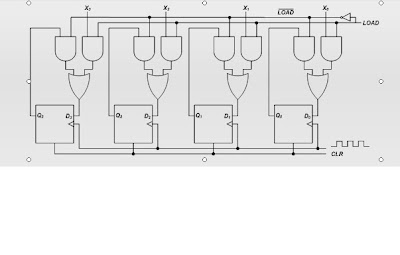

Register Buffer Terkendali dan Register Geser Terkendali

LOAD merupakan masukan kendali yang menentukan operasi rangkaian. Jika LOAD rendah, isi register tidak berubah. Jika LOAD tinggi, dengan tibanya tepi positif sinyal detak, bit-bit X dimasukkan dan data yang tersimpan menjadi jika load tinggi dengan tibanya tepi positif sinyal detak biut bit X dimasukkan dan data yang tersimpan menjadi Q3Q2Q1Q0 =X3 X2 X1 X0

Ketika LOAD kembali ke keadaan rendah, kata tersebut telah tersimpan dengan aman. Artinya, bit X dapat berubah tanpa mengganggu kata yang telah tersimpan tadi

Register Geser Terkendali

register geser terkendali (controlled shift register) mempunyai masukan-masukan kendali yang mengatur operasi rangkaian pada pulsa pendetak yang berikutnya. Jika SHL rendah maka sinyal SHL tinggi. Keadaan ini membuat setiap keluaran flip-flop masuk kembali ke masukan datanya. Karena itu data tetap tersimpan pada setiap flip-flop pada waktu pulsa-pulsa detak tiba Jika SHL tinggi, Din akan masuk ke dalam flip-flop paling kanan, Q0 masuk ke dalam flip-flop kedua, Q1 masuk ke dalam flip-flop ketiga, dst. Dengan demikian rangkaian bertindak sebagai register geser kiri.

0 komentar:

Posting Komentar